採用自我詢問與診斷功能,確保感測器資料完整性

資料提供者:DigiKey 北美編輯群

2019-03-29

感測器與物聯網 (IoT) 技術的觸角正快速延伸到工業、商業、甚至消費性市場。隨著技術的發展,確保相關感測器及其前端介面電路的資料完整性之需求越來越高。

以單一介面 IC 支援多個感測器時,資料完整性的潛在問題將變得更為嚴重,原因是一旦這個單一 IC 出問題,就可能會破壞一組讀數。這可能導致對感測到的狀況作出錯誤評估,甚至可能會讓系統作出不適當或甚至危險的動作。

本文將探討在「感測器至處理器」的訊號鏈中,導致不同硬故障與軟故障 (暫態),以及感測器讀數不準確的原因。也將介紹 Analog Devices 的高度整合 IC,並展示這款元件如何透過診斷感測器、其本身及數位 I/O 來克服這些問題。

感測器至處理器的訊號路徑

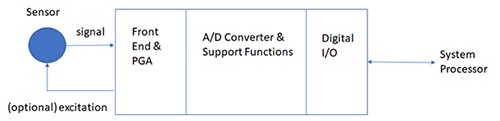

影響任何感測器讀數完整性的終極因素,都是始於圖 1 所示訊號鏈的三大主要功能區塊。這些區塊分別是:

- 感測器及其引線

- 訊號調整 IC 中的類比前端,以類比數位轉換器 (ADC) 為中心

- 連至系統處理器的數位 I/O

圖 1:基本的感測器至處理器訊號路徑原則上只包含幾個基本功能,但實用的介面 IC 可提供許多額外功能與特性。(圖片來源:DigiKey)

在多通道系統中,通常混合使用不同類型的感測器,如熱電偶、電阻溫度偵測器 (RTD) 以及壓力感測器。感測器也可能會發生故障,或者其互連引線可能會形成開路,或與相鄰引線、電軌或地線形成短路。

有些類型的感測器,在引線發生故障時會立即顯現出來,此時讀數會顯示「超出刻度範圍」。相反地,有些故障模式產生的訊號看似合理,但實際上卻不準確。此外,RTD 等有些感測器需要外部激勵電流,而且此電流必須在設定範圍內才會產生有效讀數。基於這些理由,必須對感測器及類比前端之間的訊號路徑進行連續性測試,以及檢查訊號是否維持在允許的上下限之間,並且建議使用不會受到 ADC 潛在問題影響的類比電路。

這樣不僅可以提供準確讀數,而且系統決策演算法可以依據這些讀數採用可信度極高的來源資料。

然而,所有這些額外的檢查與平衡都意味著更多的元件、更大的覆蓋區,以及更長的設計時間。

自我詢問式 IC 可確保感測器資料的完整性

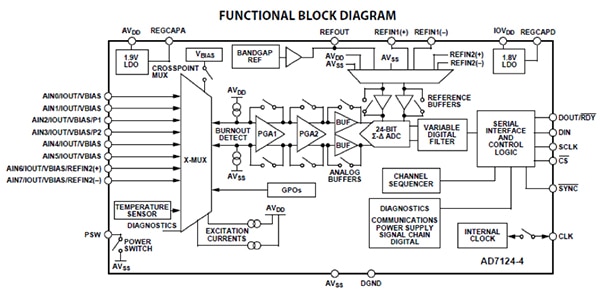

Analog Devices 推出 AD7124-8BCPZ-RL7 這款以感測器為主的 ADC 與介面,其功能遠超過基本的訊號調整與轉換,能提高資料完整性,且不會對設計時間和覆蓋區有所影響,可滿足需求。此產品包含多個訊號及自我診斷功能,可確保資料完整性。

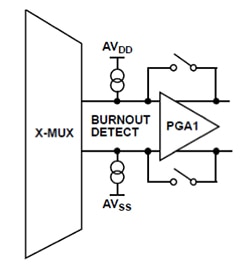

圖 2:AD7124 是以感測器為主的 ADC 與介面,其功能遠超基本的訊號調整與轉換,內含多個訊號及自我診斷相關功能,可確保資料完整性。(圖片來源:Analog Devices)

AD7124 是四通道、低雜訊、低功率、24 位元的三角積分 (Σ-Δ) 元件。取樣率範圍從略高於每秒 1 個樣本 (對許多類別的感測器及相關應用已經夠用) 一直到每秒 19,200 個樣本。在最低取樣率下,此元件耗用的電流為 255 μA。由於其設計強調低雜訊 (低於 25 nV rms),而且內部參考電壓的偏移較低 (10 ppm/°C),這款元件讀數的準確度得到提升。

AD7124 本身提供 32 引線的 LFCSP 封裝和 24 引線的 TSSOP 封裝。其數位 I/O 具有相當的靈活性,可支援 3 線與 4 線 SPI、QSPI、MICROWIRETM 以及 DSP 相容介面。

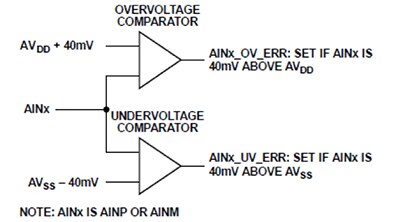

AD7124 使用兩項技術解決前述的感測器引腳問題,分別是訊號限制警報以及斷線電流偵測。訊號限制警報使用過壓/欠壓警報監控器,檢查四對類比輸入連線中每個連線的絕對電壓 (圖 3)。這個電壓必須在定義的範圍內,才能滿足規格書的要求。

圖 3:使用訊號限制警報對感測器引線進行基本驗證時,會使用具有固定最小/最大設定值的硬體式比較器。(圖片來源:Analog Devices)

斷線電流偵測使用一對互補的可編程流入與流出電流。將預先定義的電流對作為感測器引線的流入與流出電流,AD7124 便能夠驗證其完整性 (圖 4)。全開或全關的電流將切至所選的待測類比輸入線對。

圖 4:將預先定義的電流對作為感測器引線的流入與流出電流,AD7124 便能夠驗證其完整性。(圖片來源:Analog Devices)

滿量程 (或者接近滿量程) 的讀數表示前端感測器為開路。若測得的電壓為 0 V,則可能表示傳感器發生短路。錯誤暫存器會設置一個對應的標示位元,表明所發生的錯誤及錯誤類型。

最後,若使用者在應用中提供外部參考電壓 (通常是透過 RTD 或應變計完成),而不是使用內部參考電壓,AD7124 會檢查任何外部轉換參考電壓是否正確。

驗證前端和 ADC

雖然外部感測器及其引線是最有可能發生問題的地方,但確認前端/轉換 IC 本身的運作還是非常重要。可能超出規格或完全失效的功能包括:

- 內部的 ADC 參考電壓

- 可編程增益放大器 (PGA);用於放大輸入訊號,以匹配 ADC 跨度,獲得最高解析度

- 低壓降穩壓器 (LDO);用於提供所需的感測器激磁

- IC 內部電軌

- ADC 本身

為了測試訊號鏈的類比部分,AD7124 會觸發硬體與韌體式自測;隨後產生 20 mV 的訊號,而此訊號可在內部傳送到四個差動輸入通道的任何一個,然後再進行數位化。這樣做的目的有幾個:確認輸入通道多工器以及 ADC 的基本運作;透過變更 PGA 的增益設定值並檢查產生的 ADC 讀數,對 PGA 進行評估。

ADC 也可能是問題的來源之一。AD7124 採用完善的 Σ-Δ 轉換器架構,內含 1 位元調變器以及必備的數位濾波器。若要完整測試 ADC 的效能,需採用類比與數位技術。

在 AD7124 中,若調變器輸出包含 20 個連續的 1 或 0,則表示調變器對一軌或另一個軌已達飽和,而且會設置一個錯誤標示位元。同樣地,IC 會檢查 ADC 偏移係數在自我啟動的偏移校正後是否落在 0x7FFFF 和 0xF80000 之間。若在此範圍之外,就會再設置一個錯誤標示位元。最後,在滿量程校正期間,數位濾波器的任何溢位都會再設置一個錯誤標示位元。

另外,內部與外部電源及電軌也可能是問題的來源之一。許多感測器都需要少量的激磁電力,而此電力通常由類比前端 IC 的小型低雜訊 LDO 提供。

AD7124 使用兩種方式檢查 LDO 輸出;第一種方式:將 LDO 的輸出透過內部轉送至 ADC,並與預期值比較。第二種方式:使用獨立於 ADC 的硬體比較器,持續監控 LDO 相對於 IC 參考值的變化。若低於預設的閾值,則設置錯誤標示位元。因此,可在初始化期間對 LDO 進行評估,而且評估也可以持續進行,且不會持續消耗處理器資源。

為了進一步確信,可在一定程度上檢查用於監控電源供應的測試電路,即將測試電路的輸入接地 (標稱值為 0 V),然後檢查數位讀數。另外,透過檢查要求的 0.1 µF 解耦電容是否存在且已連接,AD7124 可進一步確保資料的完整性。方法是指示 AD7124 透過其內部開關中斷與解耦電容的實體連接,然後再檢查 LDO 輸出。若 LDO 的電壓下降,則解耦電容未通電。同樣地,這會設置錯誤標示位元。

當然,每個 IC 都有最高的額定溫度,若超過這個溫度,就會超出規格,甚至立即發生故障。因此 AD7124 內建有感測器,可隨時提供晶粒溫度讀數,其典型準確度為 ±0.5°C。

如何檢查數位錯誤?

截至目前為止,我們都在討論如何確保類比感測器或轉換功能的效能與準確度。然而,在電氣條件嚴苛的工業環境中會部署許多這類感測器,其中產生的問題包括雜訊、EMI/RFI,以及會對數位電子元件造成影響的暫態。因此,確保內部數位電路的效能,以及系統處理器的介面連結,以確定資料及任何讀寫作業的可靠度,便顯得相當重要。

AD7124 從以下操作及功能入手,透過多管齊下的方式達成這項要求:

- 檢查主時脈的效能;在設定輸出數據傳輸率、濾波器趨穩時間,以及濾波器限波頻率時,需要用到主時脈。主時脈可透過獨立且可隨時回讀的向上計數暫存器進行檢查。

- 透過特殊時脈計數器,檢查每個 SPI 讀寫操作使用的 SCLK 脈衝數。此數字應為 8 的倍數 (所有 SPI 操作均使用 8、16、32、40 或 48 個時脈脈衝)。

- AD7124 檢查讀寫操作是否只定址有效的暫存器位址。

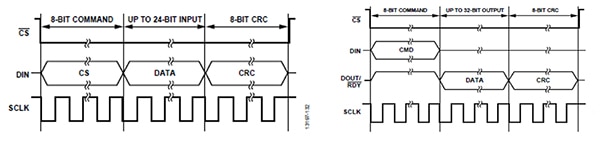

上述步驟僅解決內部操作,但無法確保處理器介面及其資料的完整性。為了提供極高可信度的資料,使用者可指示 AD7124 執行循環冗餘檢查 (CRC) 多項式核對和演算法。核對和可確保只有有效的資料才會寫進暫存器,並可驗證從暫存器讀取的資料 (圖 5)。請注意,核對和是具有高可信度的技術,甚至能偵測出單一位元的錯誤,但卻無法更正錯誤。

圖 5:將基於多項式的 CRC 核對和加至 SPI 寫入 (左) 與 SPI 讀取 (右) 交易,可偵測單一位元錯誤。(圖片來源:Analog Devices)

啟用之後,此操作會計算資料區塊上的核對和,並將其附加至每個讀取與寫入交易的末尾。為確保暫存器寫入成功,暫存器需要進行回讀,以便將儲存的核對和與依據資料計算得來的核對和進行比較。

在電氣條件嚴苛的環境中,即使是記憶體也有可能發生位元錯誤。為了對晶片上暫存器的這類錯誤進行高階檢查,AD7124 每次都會針對以下情況的運算計算核對和:

- 出現暫存器寫入週期時

- 出現偏移/滿量程校正時

- 元件執行單一轉換週期,且 ADC 在轉換完成後進入待機模式時

- 退出持續讀取模式時

為了提升可靠度,還會對內部的唯讀記憶體 (ROM) 進行評估。當電源開啟時,所有暫存器都會初始化為預設值,並儲存在 ROM 中。此時也會對 ROM 內容進行 CRC 計算。若計算出來的值與儲存的 CRC 結果不同,則表示至少有一個位元存在錯誤。

此外,AD7124 還為許多類型的感測器提供激磁,同時透過放大器和 PGA 為感測器輸出訊號提供訊號調整和擴縮。為了提供極致的可靠度,AD7124 配備有多個內部暫存器,可用來進行初始化、建立所需的功能模式和參數,以及標示不同的錯誤和故障。

使用 AD7124 評估板開啟 AD7124 的設計之旅

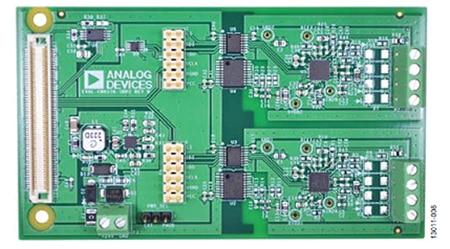

AD7124 是一個複雜系統,具有許多設計的可能性及執行能力。此元件不是簡單的「隨拿隨用」感測器介面 IC。為方便設計人員學習並且快速熟悉各種潛在功能,Analog Devices 還提供 EVAL-CN0376-SDPZ 評估板 (圖 6)。

圖 6:EVAL-CN0376-SDPZ 評估板不僅能加快導入設計的速度,還可讓 AD7124 的各項功能與特性得到充分發揮。(圖片來源:Analog Devices)

此評估板包含所需的電源供應器及外部元件,可將 AD7124 連接到多種已經實際使用的感測器及處理器。此外,評估板由以 Windows 個人電腦為基礎的 CN-0376 評估軟體提供支援,而此軟體可透過 USB 埠進行通訊,從而設定並擷取評估板中的資料。

結論

許多關鍵的決策都是由系統處理器內嵌的先進演算法做出的;如今這種決策方式在許多實例中已透過人工智慧 (AI) 得到加強。現今,更加重視這些演算法採用的原始資料是否有高度完整性可供運算,並從中得出結論及採取行動。AD7124 之類的 IC 可大幅提升資料的可信度,確保訊號鏈的每個環節 (從引線與感測器介面一直到其本身的效能與功能) 都會依照預期目標運作,並且不會受到破壞。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。