如何使用熟悉的工具在 FPGA 部署邊緣 AI

資料提供者:DigiKey 北美編輯群

2026-02-17

網路邊緣的人工智慧 (邊緣 AI) 幾乎不僅限於推論功能。實際部署通常會涉及高速輸入/輸出 (I/O)、訊號調節以及即時控制迴路,且這些全都會同時運作。這些多功能工作負載要求嚴密的協調以及不同等級的確定性,因此設計人員不容易以主流 AI 硬體滿足需求。

有兩個因素會讓問題更加複雜。首先,AI 模型正以極快的速度演進,因此設計人員必須採用可支援快速演算法更新的平台。此外,許多邊緣系統會在現場運作長達十年甚至更久,因此確保長期適應能力並不容易。其次,從模型的訓練到系統的部署,這過程仍雜亂無章。資料科學家會使用 PyTorch 和 TensorFlow,但嵌入式團隊則使用完全不同的工具鏈,這在交接過程中會造成摩擦,導致生產時間變慢。

應對這些挑戰所需的平台,要結合高吞吐量 AI 處理、確定性行為、彈性 I/O 以及長期適應性,而且必須在邊緣部署常見的受限功耗範圍內運作。

本文將重點介紹促使設計人員探索新型邊緣 AI 架構的應用與相關需求。接著會介紹具備邊緣 AI 功能的現場可編程閘陣列 (FPGA) 裝置及來自 Altera 的軟體工具,並展示如何用來滿足這些應用在各種效能與功率點上的需求。

邊緣 AI 的發展需要架構創新

邊緣系統日益採用多樣化的 AI 技術,包括用於偵測異常的傳統機器學習 (ML)、用於感知的卷積神經網路 (CNN),以及用於大型語言模型 (LLM) 的轉換器。這些運算密集型演算法通常與要求嚴格的非 AI 功能共存,例如訊號處理、連網和即時控制。

自主系統就是絕佳例子之一。經常要從多種感測器模態 (如視訊、音訊、雷達、LiDAR 和運動/位置回饋) 擷取資料、以高吞吐量進行預處理、使用先進的 AI 分析結果,然後管理高精度控制迴路,而且所有流程皆需具備可靠的確定性。

在工業自動化、醫療造影、國防和電信應用中,可找到許多類似的範例。有個常見的情況是,傳統架構難以配合融合式工作負載。

FPGA 為何特別適合邊緣 AI

相較之下,這些需求與 FPGA 的能力非常匹配。從本質上講,FPGA 提供可配置的邏輯,可達到真正的並行運算,其時序行為在設計階段即已確定,不會在運行時波動。此架構可達到低延遲確定性,這對邊緣 AI 來說相當關鍵。此彈性邏輯同時利用強大的 I/O:FPGA 通常可提供大量高速 I/O,能與多種感測器和致動器介接,能與 AI 處理緊密結合。

FPGA 也包含分散式內部記憶體,可將資料保留在靠近資料運算的邏輯所在之處。這可減少多個處理階段必須爭用共用記憶體匯流排時所產生的瓶頸,這在處理器架構中是一項常見的限制。

許多 FPGA 也包含專門的數位訊號處理 (DSP) 硬體。這些強化電路比起一般用途架構,可在訊號處理工作負載上提供更高的效能與更優異的能源效率。某些 FPGA 也整合了固線式處理器系統,可以運行標準軟體堆疊,包括 Linux,因此可針對像是連網、裝置管理與使用者介面等任務,達到傳統的軟體開發。

簡而言之,單一 FPGA 就可統整原本可能需要個別 I/O 晶片、AI 加速器、DSP及控制平面處理器的功能。如此一來,就可減少物料清單 (BOM)、縮小電路板佔用面積,並且降低功耗,同時維持邊緣 AI 應用所需的低延遲和確定性。

AI 張量區塊的加入如何開啟新可能性

傳統的 FPGA DSP 硬體就已經非常適合許多邊緣工作負載,但 AI 推論往往以高密度但低精度的乘加運算為主。為了解決這個問題,Altera 的 Agilex 3 和 Agilex 5 裝置配備了增強型 DSP 及 AI 張量區塊。這是專門用於矩陣對矩陣、以及向量對矩陣相乘的專用硬體,這類運算在 AI 運算圖中會反覆出現。

這種做法的核心是純量積以及加法器/累加器引擎 (圖 1)。在張量模式中,固線式點積引擎會使用 8 位元輸入和預載的 8 位元權重,執行 10 元素點積。為了擴大動態範圍,資料路徑也可以使用共享的「共用指數」來進行區塊浮點式縮放,以解決 AI 推論通常需要高動態範圍但低精度的情況。

圖 1:AI 張量區塊可執行 10 元素點積運算。(圖片來源:Altera)

圖 1:AI 張量區塊可執行 10 元素點積運算。(圖片來源:Altera)

點積結果為 32 位元 (定點或單精度浮點),並且可以串接至額外的加法器/累加器階段,以計算跨鄰近區塊的較大點積。每個 AI 張量區塊包含兩個點積欄位,可達到多種運算模式。

在典型使用情境中,有些增強型數學硬體會用於傳統的 DSP 功能,例如對雷達資料執行快速傅立葉轉換 (FFT)。其他則當作 AI 張量區塊使用,例如用 CNN 進行物件偵測。這種靈活性對於必須同時處理 AI 與其他高運算密集功能的邊緣系統來說相當關鍵。

適合不同 AI 工作負載的多種 FPGA 選項

Agilex 系列在效能擴充方面提供相當大的彈性。元件涵蓋從僅 12 mm × 12 mm 且注重效率的裝置,到每秒高達 152.6 峰值兆次運算 (TOPS) 的高效能型號,且在 I/O 與記憶體介面能力方面都具有相似的擴充能力。

有個高效能零件範例是 Agilex 5 A5ED065BB32AE4SR0,其以 32 × 32 mm 封裝提供 22.17 TOPS。效率導向的零件範例則是 Agilex 3 A3CW135BM16AE6S,能以 16 × 16 mm 封裝提供 2.8 TOPS。主要規格如表 1 所示。

|

表 1:此為 Agilex 5 及 Agilex 3 範例 FPGA 的一些主要規格。(表格來源:Altera (經作者修改))

這兩個系列均有傳統 FPGA 版本,或是搭載整合式 Arm 處理器的系統單晶片 (SoC) 版本。Agilex 3 SoC 含有雙核心、800 MHz 的 Arm Cortex-A55。Agilex 5 SoC 具有非對稱叢集搭配雙核心 1.8 GHz Cortex-A76 以及雙核心 1.5 GHz Cortex-A55。這兩種配置都支援 Linux,因此能針對連網、裝置管理與使用者介面進行傳統的軟體開發。

使用 FPGA 簡化邊緣 AI 部署

AI 模型通常會在以軟體為中心的框架中開發,且迭代週期迅速,而 FPGA 實作歷來都需要具備硬體開發技能且整合週期較長。Altera 的 FPGA AI Suite (圖 2) 提供更直接的途徑,能以相容於業界標準 AI 工具的流程,將訓練好的模型轉換成可部署的 FPGA 推論智慧財產權 (IP)。

圖 2:FPGA AI Suite 的工作流程可將標準 AI 框架與 FPGA 部署銜接在一起。(圖片來源:Altera)

圖 2:FPGA AI Suite 的工作流程可將標準 AI 框架與 FPGA 部署銜接在一起。(圖片來源:Altera)

工作流程可總結如下:

- 使用 PyTorch、TensorFlow 或 ONNX 等標準架構來開發推論模型。

- 使用 OpenVINO 工具組將模型轉換成由圖形檔案 (.xml) 及權重檔案 (.bin) 組成的中介碼 (IR)。

- 將 IR 作品傳送到 FPGA AI Graph Compiler,就可將此模型對應到可用的 FPGA 資源。此類資源包括外部主機處理器、內部處理器或無頭端的配置。

- 使用 Quartus Prime Pro Edition 編譯並部署生成層,執行過程則由推論引擎執行階段堆疊以及FPGA AI 應用程式介面 (API) 進行管理,以達到記憶體搬移與硬體排程。

- 在編譯過程中,可使用 Architecture Optimizer 來平衡效能與資源的使用。例如,可用來確保實作符合推論的吞吐量目標,同時保留其他 FPGA 邏輯的空間。

在實務上,這種做法的價值在於可將「在 FPGA 上部署」轉變為一個整合過程,而非加速器的設計工作。資料科學家可以專注在既定的模型開發工作流程中,同時 FPGA 和嵌入式團隊會收到自然適合建置與部署週期的作品,因此可隨著模型與需求演進加快迭代速度。可利用 OpenVINO 工具組的 Open Model Zoo 提供的預訓練模型進一步加速開發。

使用容易操作的開發套件快速入門

若要開始在 FPGA 上探索邊緣 AI,設計人員有多種開發套件選擇。針對高效能應用,Terasic 的 P0775 Atum A5 開發套件 (圖 3) 是不錯的選擇。此套件以 Agilex 5 A5ED065BB32AE4SR0 為核心,可提供適合邊緣級系統的多樣化介面。主要功能包括 8 GB DDR4 記憶體、QSFP+ 和 2.5 Gbit 乙太網路 (GbE) 埠、PCIe Gen 3 x4、雙重 MIPI 相機連接器,以及 HDMI 輸出。此套件含有 Quartus Prime Pro Edition 的免費授權。

圖 3:P0775 Atum A5 開發套件可進行高效能的 AI 與視覺開發。(圖片來源:Terasic)

圖 3:P0775 Atum A5 開發套件可進行高效能的 AI 與視覺開發。(圖片來源:Terasic)

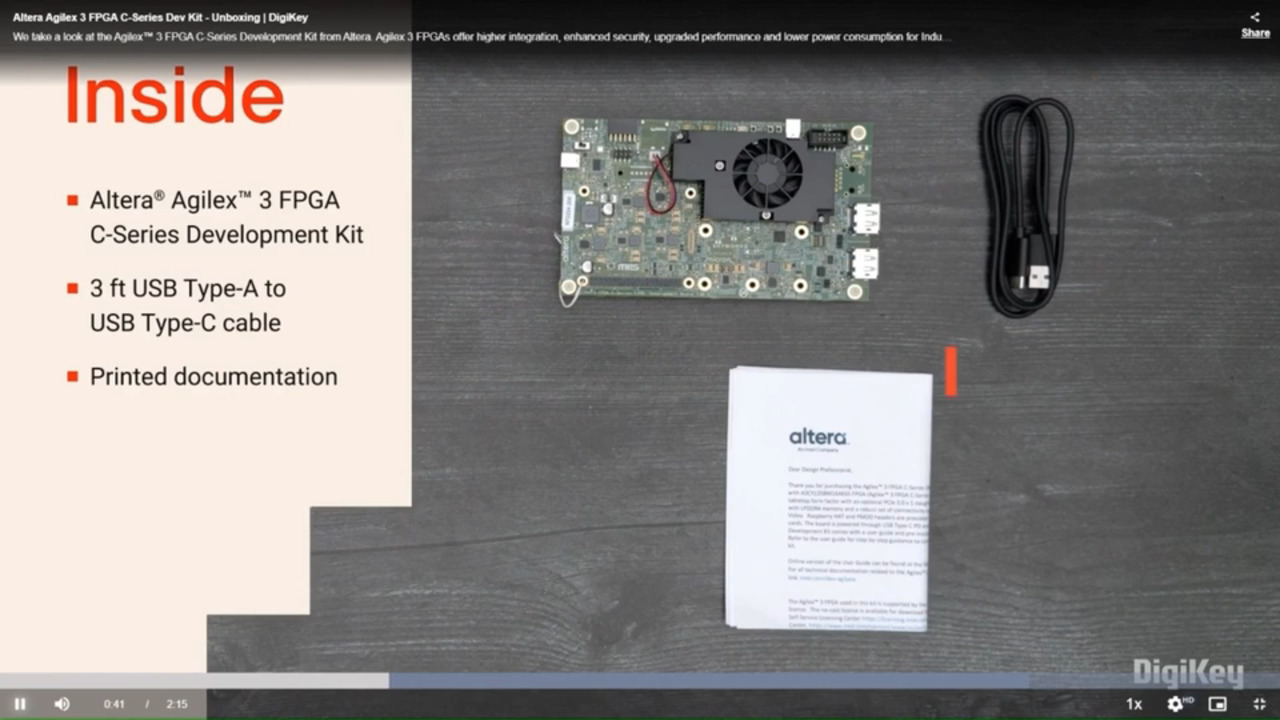

若是注重效率的應用,設計人員可轉用 DK-A3W135BM16AEA Agilex 3 FPGA 與 SoC C 系列開發套件 (圖 4)。此套件以 Agilex 3 A3CW135BM16AE6S 為核心,強調具備生態系統友善擴充的緊湊型原型設計。此板件提供 4 GB 的 LPDDR4、GbE、DisplayPort 和 USB 2.0,並配備 Raspberry Pi HAT 連接器,以及 Digilent Pmod 介面,可順利進行擴充。

圖 4:DK-A3W135BM16AEA Agilex 3 FPGA 與 SoC C 系列開發套件,提供適合注重效率型邊緣 AI 的緊湊型平台。(圖片來源:Altera)

圖 4:DK-A3W135BM16AEA Agilex 3 FPGA 與 SoC C 系列開發套件,提供適合注重效率型邊緣 AI 的緊湊型平台。(圖片來源:Altera)

結論

邊緣端引進 LLM 及其他新型 AI 工作負載,促使開發人員尋求新的作法。FPGA 可提供獨特的解決方案,不僅具備低延遲且確定性的效能,還能處理其他許多系統功能。透過具備 AI 功能的 Agilex FPGA 及 FPGA AI Suite,開發人員可輕鬆快速地運用這些功能,開創新的架構可能性,達到高度適應且壽命長久的設計。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。