透過多核心處理器達到多種功能與安全要求

資料提供者:DigiKey 北美編輯群

2020-10-01

汽車、工業、機器人、大樓控制以及其他關鍵嵌入式系統應用預期將會承擔更多元的工作負載,包括低功率即時監測,以至於針對人機介面 (HMI) 採用多螢幕圖形顯示的高階多媒體應用。除了達成這些廣泛的功能要求,這些應用還必須能支援嚴格的安全標準、更低的成本與覆蓋區,並達到最佳的功率/效能平衡。

為了符合這些有時互相衝突的要求,開發人員至今被迫犧牲功能性,或是讓設計和製造變得很複雜,因為需要使用更多的元件,來支援圖形、保全、安全等方面的特定要求。開發人員真正需要的是只靠單一解決方案,就能在廣泛的關鍵嵌入式系統應用中支援各種產品達成這些要求。

本文將簡單說明關鍵嵌入式系統設計的演進歷程。接著會展示如何使用 NXP Semiconductors 特別設計的多核心應用處理器,來解決開發人員面臨的挑戰。在廣泛功能性與安全認證能力方面,這些處理器能支援一系列快速增多的要求。

嵌入式系統設計演進的考量事項

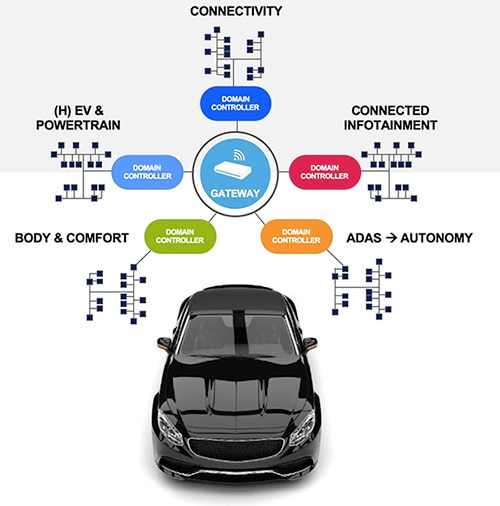

嵌入式元件的傳統角色為支援一組有限系統功能,這已被大幅取代,目前要求元件能提供廣泛的功能。例如在工業應用中,由於智慧型工具和設備的 HMI 能力需要增強,這就要求處理器能夠提供經過最佳化的圖形,同時符合更多傳統的工業即時要求。同樣地,汽車應用趨於採用以功能領域叢集和閘道構成的階層式架構,這就推動處理器必須能夠完全符合這些要求 (圖 1)。

圖 1:隨著趨於採用階層性更高的汽車系統架構,已然形成對整合度更高之可擴充處理器解決方案的需求。(圖片來源:NXP Semiconductors)

圖 1:隨著趨於採用階層性更高的汽車系統架構,已然形成對整合度更高之可擴充處理器解決方案的需求。(圖片來源:NXP Semiconductors)

在每個功能領域中,由於需要更複雜的功能,效能與整合式功能的門檻也不斷提高。舉例來說,抬頭顯示器的興起,需要能確保為駕駛員持續提供重要圖形資訊的解決方案。除了這些下一代顯示器外,隨著駕駛員需要具備更越來越高的警覺性,對攝影機介面的要求已有所增加,以及需要以高效能的方式,執行能提供睡意偵測的進階辨識軟體。

隨著應用持續進化發展,對高整合性可擴充解決方案的需求也變得更加迫切,以便符合越來越多元的要求,同時將設計覆蓋區、成本與複雜性降到最低。藉助 NXP 的 i.MX 8 系列應用處理器,開發人員能利用相容的處理器平台以及一系列所需的功能與效能,來支援各種應用要求。在 NXP 的 i.MX 8 系列中,針對中階汽車與工業應用,i.MX 8X 系列能解決近來出現的安全認證處理器需求

多核心架構能管理多種工作負載

在實作汽車與工業應用元件時,開發人員面臨的困難之一是需求的多樣化。開發人員原先預期分別應對即時或高階應用處理工作負載,但對智慧型子系統的要求卻將這些極為不同的運算類型合併在一起。開發人員越來越需要這樣的解決方案,以提供可靠的即時回應和高效能應用執行,又能支援功能安全要求。

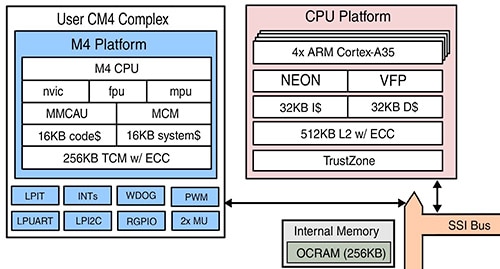

NXP 的 i.MX 8X 系列處理器專為提供即時能力、高效能處理與低功耗所設計,充分利用複雜的多核心中央處理單元 (CPU) 架構,來管理多種運算工作負載 (圖 2)。

圖 2:NXP 的 i.MX 8X 系列採用多核心架構,包含 Arm Cortex-M4 (CM4) 嵌入式處理器和多個 Arm Cortex-A35 應用處理器,以支援各種軟體工作負載。(圖片來源:NXP Semiconductors)

圖 2:NXP 的 i.MX 8X 系列採用多核心架構,包含 Arm Cortex-M4 (CM4) 嵌入式處理器和多個 Arm Cortex-A35 應用處理器,以支援各種軟體工作負載。(圖片來源:NXP Semiconductors)

對於一般用途的即時處理工作,i.MX 8X 元件含有 Arm Cortex-M4 (CM4) 處理器,搭配浮點單元 (FPU)、記憶體保護單元 (MPU)、記憶體對應加密加速單元 (MMCAU) 和其他控制模組 (MCM)。為了支援感測器和致動器等外部周邊裝置,這款使用者 CM4 複合體結合了巢式向量中斷控制器 (NVIC) 和全套介面與模組,包括低功耗定期中斷計時器 (LPIT)、脈寬調變 (PWM),以及汽車和工業應用中通常需要的其他功能。一對快閃記憶體和具備錯誤修正碼 (ECC) 能力的緊密耦合記憶體 (TCM),有助於盡量減少對外部記憶體的存取、加快執行速度,以及應對記憶體錯誤。

為了快速執行應用工作負載,此 CPU 平台包含多個高能效的 Arm Cortex-A35 應用處理器 (AP),其中兩個 AP 位於 8DualXPlus 處理器中,如 MIMX8UX6AVLFZAC,四個 AP 位於 8QuadXPlus 處理器中,如 MIMX8QX6AVLFZAC。除了專屬的指令 (I$) 和資料 (D$) 快取,此 CPU 平台還包含帶有 ECC 的 512 KB 第二階 (L2) 共享快取。

此架構的 Arm Cortex-A35 核心同時提供軟體相容性與效能擴充能力,並支援 32 位元向下相容性與 64 位元效能。為了進一步加速執行訊號處理和機器學習等運算密集型演算法,Arm Cortex-A35 處理器提供向量浮點 (VFP) 處理,以及 Arm 的 Neon 單指令多資料 (SIMD) 架構擴充元件。為了在影像處理、電腦視覺和機器學習方面加快軟體的執行速度,Arm 運算函式庫提供針對 Arm 處理器及圖形處理單元 (GPU) 架構進行最佳化的函數,而開放原始碼 Ne10 C 資料庫則為運算密集型作業,提供一些經過 Arm 最佳化的函數。

專屬引擎為主要 CPU 卸除負載

除了使用者 CM4 複合體和 Arm Cortex-A35 多核心 CPU 平台之外,此架構還提供額外的專屬引擎,以用於多媒體應用。此架構包含數位訊號處理器 (DSP) 進行音訊和語音編解碼器處理,同時還整合 GPU 與影片處理單元 (VPU)。元件的 GPU 支援標準圖形資料庫,並利用四個個別的四分量浮點向量 (vec4) 和 16 個執行單元,以及高效能的 2D bit blit 引擎,來加快作業速度。VPU 可處理常見的影片格式,加速解碼高達 4Kp30 (逐行,30 Hz) 的影片,以及加速編碼高達 1080p30 的影片。晶片的專屬顯示器控制器區塊,進而能將圖形輸出驅動至多達三個獨立的顯示器。

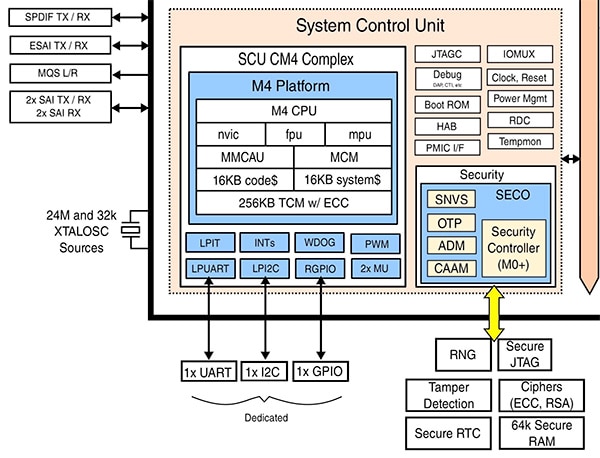

為了進一步將效能最大化,i.MX 8X 架構還整合額外的處理器核心,專門用來在執行系統管理和安全服務時,為主要 CPU 平台卸除通常會出現的額外處理負載。對於系統管理,此架構的系統控制單元 (SCU) 整合一個 CM4 複合體,與使用者 CM4 複合體相配,但會保持完全專屬於 SCU 作業,而無法供開發人員使用 (圖 3)。

圖 3:SCU 深度整合於 NXP 的 i.MX 8X 處理器內,且無法供開發人員使用。本身利用專屬的 Arm Cortex-M4 (CM4) 子系統,為元件的主要處理器卸載系統管理工作。(圖片來源:NXP Semiconductors)

圖 3:SCU 深度整合於 NXP 的 i.MX 8X 處理器內,且無法供開發人員使用。本身利用專屬的 Arm Cortex-M4 (CM4) 子系統,為元件的主要處理器卸載系統管理工作。(圖片來源:NXP Semiconductors)

除了管理電源、時脈及其他內部功能,SCU 還控制正常作業中的引腳多工和輸入/輸出 (I/O) 通道驅動強度。事實上,使用者 CM4 複合體和 Arm Cortex-A35 AP 都無法直接存取這些各式各樣的低階硬體功能。而 SCU 可用於將這些功能抽象化,因此在使用者 CM4 或 AP 上執行的軟體,只需要調用 SCU 的韌體應用程式開發介面 (API) 函數,即可執行將非必要的電源域斷電之類的功能。舉例來說,如果該電源域正在與另一個處理器共享,SCU 只需確認斷電請求,但維持電源域的供電,直到另一個處理器也發出斷電請求為止。

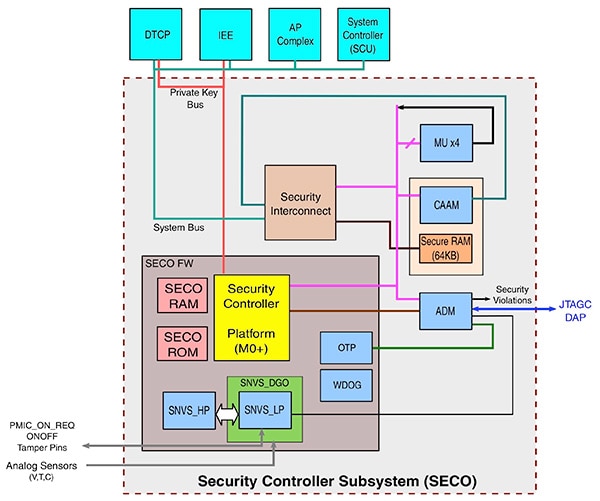

為了管理 i.MX 8X 元件對安全性的廣泛支援,另一個專屬處理器會在元件的安全控制器 (SECO) 子系統中發揮作用。在 SECO 子系統中,整合式低功耗 Arm Cortex-M0+ 處理器會執行韌體以支援多項硬體型安全功能,包括安全金鑰的私人匯流排存取、一次性可編程 (OTP) 記憶體供安全儲存金鑰,以及安全非揮發性儲存裝置 (SNVS) 供存放額外的私人資料或臨時金鑰 (圖 4)。

圖 4:在 NXP 的 i.MX 8X 安全控制器 (SECO) 子系統內,專屬的低功耗 Arm Cortex-M0+ 處理器會管理安全性作業,利用私鑰匯流排和多重硬體模組進行安全儲存、加密加速,以及經過驗證的偵錯存取。(圖片來源:NXP Semiconductors)

圖 4:在 NXP 的 i.MX 8X 安全控制器 (SECO) 子系統內,專屬的低功耗 Arm Cortex-M0+ 處理器會管理安全性作業,利用私鑰匯流排和多重硬體模組進行安全儲存、加密加速,以及經過驗證的偵錯存取。(圖片來源:NXP Semiconductors)

除了這些核心安全機制,SECO 子系統也會協調安全性作業,以進行透過經驗證的偵錯模組 (ADM) 協調的竄改偵測和安全偵錯。在安全執行方面,整合的加密加速與保證模組 (CAAM) 硬體安全模組支援整套安全性演算法,包括對稱與非對稱加密、雜湊函數及亂數數字產生器 (RNG)。

在正常作業中,元件處理單元包括 SCU、AP 和數位傳輸內容保護 (DTCP) 加速器,都會使用 SECO 安全互連,透過系統匯流排來存取 CAAM 功能。除了透過 CAAM 直接記憶體存取 (DMA) 功能進行存取,SECO 的專屬 Cortex-M0+ 處理器無法存取系統匯流排。反之,此處理器使用受到保護的內部連線來存取周邊裝置、安全隨機存取記憶體 (RAM)、唯讀記憶體 (ROM),以及本身特殊的私鑰匯流排。

除了使用 DTCP 加速器,此私鑰匯流排在 i.MX 8X 處理器支援快速加密和解密時,也會扮演核心角色。在此,安全處理器使用自身的資源來提供元件的直列加密/解密引擎 (IEE) 模組所需的私鑰,因為其會安全地讀取或寫入經過加密的儲存空間,無需請求處理器、DMA 控制器或 I/O 元件涉入其中。

以元件 Cortex-A35 處理器內建的 Arm TrustZone 技術作為建構基礎,SECO 子系統在安全啟動程序中也搭配 SCU 一起使用。在此程序裡,SCU 會解譯啟動設定、配置啟動來源,並將啟動映像檔載入到內部或外部記憶體。SECO 子系統則利用其加密函數,在簽署過的韌體映像檔載入後但執行之前,對這些映像檔進行驗證。

保護關鍵的顯示器與控制功能

雖然能安全有效地處理多種工作負載很重要,但對一些關鍵任務應用來說,保護關鍵功能的能力一樣非常重要,例如汽車與工業領域中的一些應用。NXP 的 i.MX 8X 系列將本身的處理能力,與符合這些關鍵要求所需的安全認證能力結合在一起。

此處理器系列的安全性支援係建構於多個層級,最開始是透過全空乏絕緣上覆矽 (FD-SOI) 製程技術進行製造,旨在強化系統可靠性。由於系統的安全仰賴於完備的安全基礎,因此結合支援 TrustZone 的 AP、SECO 子系統和安全啟動功能,可提供反制安全與保全威脅所需藉助的受信任環境類型。

同時,當能透過使用者 CM4 複合體來獨立處理時間緊迫的工作,並將關鍵的系統工作卸載至 SCU 和 SECO 子系統時,這會有助於確保即便是處理負載不斷發生變化,仍能提供關鍵任務型應用功能。事實上,NXP 將此概念進行延伸,透過自家的 SafeAssure 技術支援任務關鍵型顯示器。此技術將支援汽車安全完整性 B 級 (ASIL B) 的硬體顯示器容錯移轉路徑,整合於 i.MX 8X 元件中。有了 SafeAssure,如果元件偵測到資料完整性或 GPU 錯誤,即會自動為使用者提供容錯移轉映像檔。此容錯移轉映像檔會在背景中執行,可確保即使在主顯示器故障時,仍能提供關鍵的資訊。

在 i.MX 8X 型系統中,對安全應用的支援延伸至記憶體存取。在所有支援的記憶體介面中,i.MX 8X 元件為雙倍數據傳輸率 3 低電壓 (DDR3L) 記憶體提供 8 位元 ECC。除了 L2 快取內的 ECC (請再次參見圖 2),此 DDR3L ECC 功能還支援工業安全完整性 3 級 (SIL 3)。此外,i.MX 8X 架構也將 ECC 支援性延伸至外部快閃記憶體儲存裝置。在此,整合的 Bose、Ray-Chaudhuri、Hocquenghem (BCH) 編碼器和解碼器模組提供 62 位元 ECC,其能針對從這些儲存裝置讀取的資料模塊,修正當中 2 至 20 個單一位元錯誤。

啟動 i.MX 8X 型應用

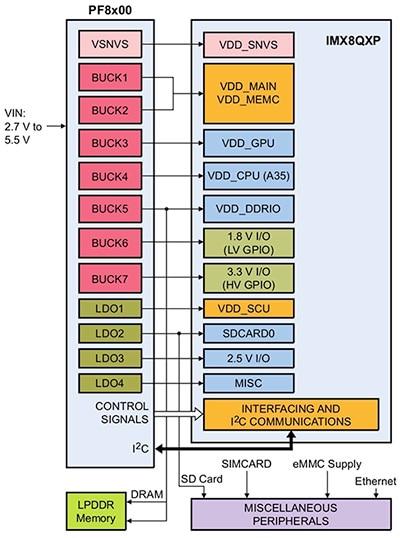

和任何此等級的處理器一樣,在實作 i.MX 8X 型設計時,需要小心留意嚴格的電源要求,包括關鍵電源啟動順序。要啟動 i.MX 8X 元件的電源,需要依照順序或同時啟動四個不同的電源組別,首先是 SVNS 子系統,接著是 SCU、I/O 和記憶體介面,最後是元件剩餘的部分。只要使用 NXP 的 PF8x00 電源管理積體電路 (IC) 元件,開發人員就能滿足此需求。該元件提供支援 i.MX 8X 處理器所需的全套電軌與控制訊號,以及外部記憶體和典型的系統周邊裝置 (圖 5)。

圖 5:NXP 的 PF8x00 PMIC 提供驅動 i.MX 8X 處理器所需的全套電軌與控制訊號。(圖片來源:NXP Semiconductors)

圖 5:NXP 的 PF8x00 PMIC 提供驅動 i.MX 8X 處理器所需的全套電軌與控制訊號。(圖片來源:NXP Semiconductors)

在實作自己的 i.MX 8X 型設計時,開發人員可以使用 NXP 的 MC33PF8100CCES PMIC,此電路事先經過編程,能與 MIMX8QX6AVLFZAC 等 8QuadXPlus 處理器搭配使用。MC33PF8100A0ES 和 MC33PF8200A0ES 等其他 PF8x00 機型,均支援 i.MX 8X 處理器,但並未事先編程。

對於安全應用,MC33PF8200A0ES 等 PF8200 系列元件整合一些特點,專門用於支援 ASIL B 系統。除了多個內部監視器,包括具有專用帶差參考電壓的輸出電壓監視器,PF8200 PMIC 還包含自動防故障輸出 (FSOB) 引腳,以讓系統在電源啟動期間或在電源故障事件中,持續處於安全狀態。此外,類比內建自我測試 (ABIST) 常式會測試所有電壓監視器,而自我測試常式會確認其他元件功能性。

雖然 PF8x00 PMIC 能簡化 i.MX 8X 型系統的硬體設計,但有些開發人員可能需要立刻開始評估 i.MX 8X 元件,並迅速開發 i.MX 8X 型應用的原型。NXP 的 MCIMX8QXP-CPU i.MX 8X 多重感測器支援套件 (MEK) 提供一個就緒型開發平台,結合 NXP 的 i.MX 8QuadXPlus 處理器、NXP 的 F8100 PMIC、3 GB RAM、32 GB 嵌入式多媒體控制器 (eMMC) 記憶體,以及 64 MB 快閃記憶體。除了顯示器、攝影機和音訊介面,MEK 板還包含一組通常用於汽車或工業應用的感測器。若想取得額外的連線能力、音訊和擴充選項,開發人員也可以添購 NXP 選配的 MCIMX8-8X-BB 基板。

結論

在汽車、工業、大樓控制和 HMI 等越來越多的應用中,處理工作負載類型不斷增多,包括傳統的即時 I/O 處理,以及新興的多媒體圖形應用層級處理。雖然每種工作負載類型都存在一些設計選擇,但隨著越來越需要藉由解決方案獲得高效能表現和省電效率,以達到汽車與工業應用中的安全認證設計要求,目前還很少有解決方案能滿足這種需要。

如本文所示,使用 NXP Semiconductors 的多核心處理器系列,開發人員可以更有效地實作滿足需求的設計,既能達到這些各式各樣的要求,又能輕易擴充以應對高效能方面的新興要求。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。